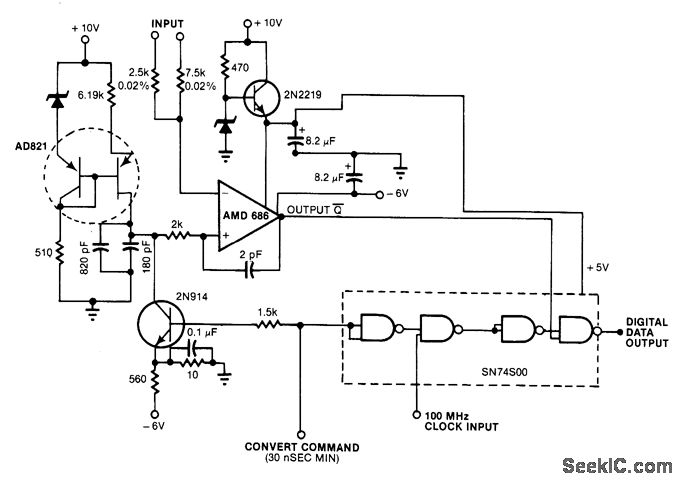

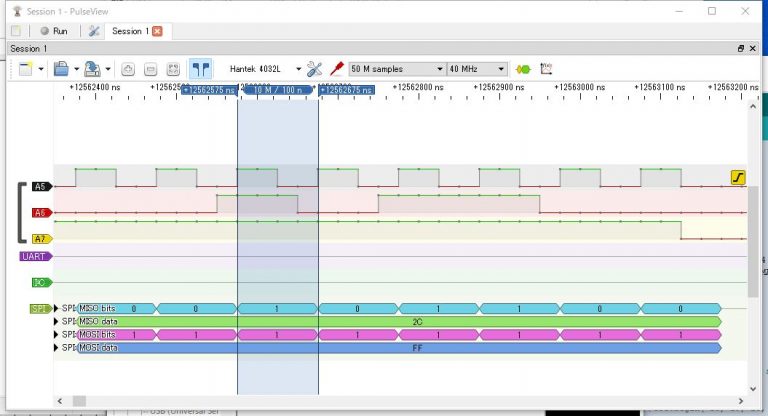

This condition may seriously affect the device and will be an error in bitstream creation. To prevent the reference clock frequency from rising too high, it is necessary to lower. PhysDesignRules:2452 - The IOB q is either not constrained (LOC) to a specific location and/or has an undefined I/O Standard (IOSTANDARD). On our configuration, we achieved a stable BCLK Frequency of 148 MHz with no USB- or SATA-related issues. A 100Hz 12dB/octave high-pass filter affects both mic and line inputs and comes before the. Then, we calculate the size of the register that will hold this count. So the clock cycle is repeated 10M times in 0.1 second. To to create a 0.1 second delay, we multiply the clock with the required time: 100MHz 0.0000. An on-board 100 MHz oscillator, IC17, Fox 767-100-136, supplies the PL subsystem clock input on bank 13, pin Y9.īut when I allocate NET "clk" LOC = Y9, it seems doesn't work! I can't find where the clk is! There suppose to be a button or something that I can control, right? Photo: Mike CameronAllen & Heaths ZED R16 is their first new. Basys 3 has a 100 MHz clock which means that the clock cycle is repeated 100M times in one second. The PS infrastructure can generate up to four PLL-based clocks for the PL system.

#100 mhz clock mini zed series#

The EPP’s PS subsystem uses a dedicated 33.3333 MHz clock source, IC18, Fox 767-ģ3.333333-12, with series termination. Clock Generators & Support Products 1.5-1.8 V 12-output PCIe Gen 1/2/3/4 + 25 MHz LVCMOS clock generator, with 100 internal termination Si52212-A01AGM Skyworks Solutions, Inc. So I looked up the document ZedBoard_HW_UG_v1_1.pdf. But it seems wrong to allocate "clk" to a user switch. When I allocate the pin, I want to have a clock. I'm writing a counter in VHDL, and try to implement it on the Zedboard Zynq 7000 XC7Z020-1 CSG484CES EPP.

0 kommentar(er)

0 kommentar(er)